デジタル オシロスコープ 自作の検討

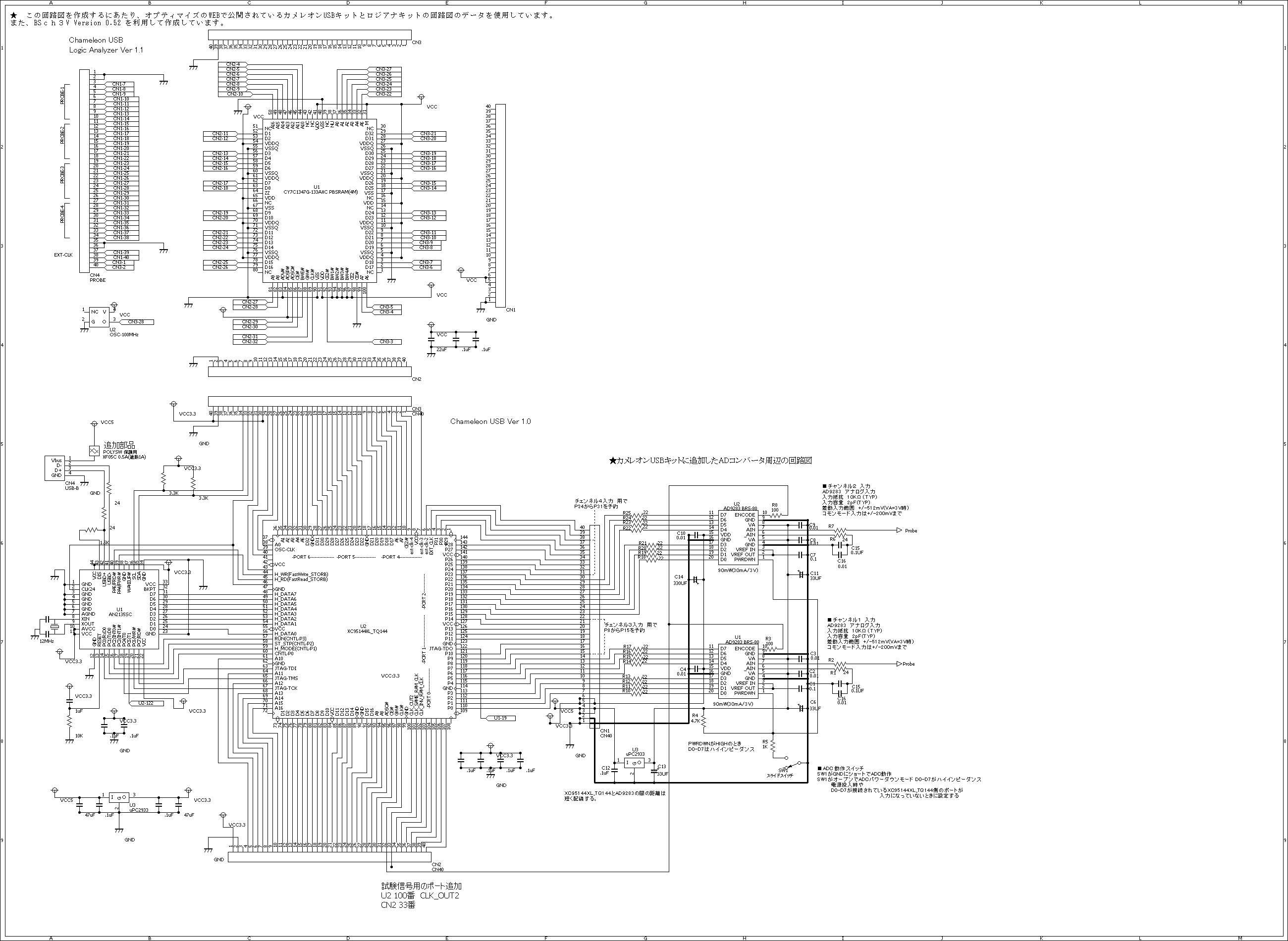

既製品のデジタルオシロを購入することが最良であるとの結論であるが、オプティマイズ(販売業者名)のカメレオンUSBキットとロジアナキット(4M)を

利用してADコンバーターを外付けして簡易的なものができないかどうかを検討してみることにした。このキットは、PCとUSB接続して使う32チャンネル

のロジックアナライザーで、最高100MHzで128Kメモリーできるものである。

検討はじめとして、このキットに、単に8ビットの80MSPSのADコンバーター AD9283-80を2個つないでみた。

オシロスコープの内容としては、入力2チャンネルで、早さは50MSPS、記憶量は128Kサンプル、AD変換は8ビットだが実際に使える精度は5~6

ビット程度、トリガレベル

は16段階でSINGLEモード、入力アナログ帯域幅約8MHz(実測していないのでうそかほんとうか分からない)と言うものである。

回路編

そのほか、AD入力のアンチエイリアスフィルターや ハイインピーダンスの入力電圧範

囲切り替え用の回路や PCと被測定物との間の(GND)アイソレーションなど が無く、

また、 理論上の理想値でもアナログ入力周波数バンド幅がだいたい8MHzしかないなど、

このままでは実用的には使えるものではない。

今回 使用したADコンバーターの入力抵抗は10KΩ(TYP)となっているが、実際には、ドライブ側の出力インピーダンスが たとえば25Ωなど 低い

値で動かしてやらないと 上手く動かないようだ。ドライブ側の抵抗値が大きいと、零入力でもデジタルデータは零にならずオフセットをもち、その値は

ENCODEの動作周波数に依存して値が大きくなる現象が見られた。ADコンバーターのアナログ入力の周囲で~数十MHzの信号が飛んでいるので、その影

響も受けているようだ。

ソフトウエア編

ロジアナキットのCPLDのソフトを一部改造し、波形表示するためのソフトを試作してみた。

AN2135SCのファームはロジアナキットのものをそのまま使い、オシロスコープ用にCPLD(XC95144)のVHDLプログラムは4Mbitキッ

ト

のものから一部変更を加えた。

CPLD(XC95144)のVHDLの主な変更点は、

・試験測定用に100番ピンから1MHzの信号がでるようにした。 (下図左が

1MHzの信号を観測した例。サンプリング周波数が50MHzの時、入力抵抗R2,R7は55KΩとしたがこれは暫定値。 サンプリング周波数

100MHzでは上手く行かなかった。)

・トリガ条件に使用するプローブの選択をトリガレベルの設定に変更。(設定できるレベルは16段階のみ。8ビットの256を16分割した。かつ、トリガの

入力はチャンネル1しか選択できな

いなどの制約あり。)

・一度 PBSRAMに128Kサンプル分の入力データを書き込んだ後からトリガ検出動作を開始する、コントロールソフトから設定するビット

P_ONE_CYCLE_WRITE を新たに追加。 (計測を開始するとPBSRAMはリングバッファになって入力データを蓄積していく。トリガの検出

手前のデータも見たいので、一回分ためておく機能を追加した。)

もう少し追加したい機能もあったが、CPLD(XC95144)の容量?の上限で、もうあまり入らないようだ。

波形を表示するためのソフト(574,464 バイト)は、ロジアナコントロールソフト

を参考にさせて頂きながら、(VCができないため) C++Builder 5

でつくり直した。下図右はI2C通信の例で、上がクロック波形で、下がデータ波形である。

波形にぎざぎざのノイズが乗っているが、これは、きっと配線(SOP28ピン変換基板+空中配線で基板化していないし)や回路構成やGND側の構成が悪い

ためであろう。AD

コンバータの精度と

しては5~6ビット程度しかでていない。

細い波形観測は無理だ、せいぜい、おおまかなことしか観測はできそうにない。

サンプリング周波数100MHzでは波形に不要なひげが出て上手く動かない(今回のADコンバータのスペックは80MSPS)。 50MHzが最高のサ

ンプリング周波数とな

る。

アナログのコンポジットビデオ信号

参考に アナログのビデオ出力の波形を見てみた。

ビデオ測定用のADコンバータの入力の回路は

こんな感じである。ビデオ信号なので75Ωの低い抵抗で受けている。

下図左が1ライン分の波形、下図右がカラーバースト信号を拡大してみたもの。本当はもっと綺麗な波形(たとえば、カラーバーストは本来は約3.58MHz

の正弦波)

である。カドカドになってしまってノイズに埋もれ

てしまっているのは正しい姿ではない。

ノイジーな波形だ。

■参考になる資料

■警告

・この検討品で使用しているオプティマイズ(販売業者名)のロジア

ナキット(4M)をロジアナキットのCY7C1347G-133AXC

の半田付けは難しいです。 隣のリード間と半田ブリッジした場合 半田吸い取り が必要です。

・XPへの カメレオンUSBキットのezusbのドライバーのイ

ンストールは、オプティマイズのWEBで公開されている <上記ドライバーが正常に動かない場合> の手法で行った。

・カメレオンUSBキットのXC95144XL_TQ144の接続ポートとADコンバータAD9283のD0~D7端子が互いに出力状態になるとIC

の破壊が起きます。 D0~D7をフローティングさせるために USBから

の電源ON/OFF時またXC95144へのJED書き込み時など 適時 スラ

イドSW1を人間が切り替えて使用しています

・PCと被測定物がアイソレーションされていない場合、電位差などにより電

流が流れて機器の破壊が起きることがあります。 あらかじめ、PCと被測定物との間の電位差を測定確認するなどして、十分注意してください。

・ADコンバータに定格を越えた入力をすると、ADコンバータが破壊する恐

れがあります。

・ADコンバータ回路を追加することによりUSBからのVBUS+5V電源の負荷

が増加します。 安全のためVBUS回路に過電流保護素子の

ポリスイッチを追加しました。

・D0~D7やCLK(ENCODE)などnSオーダーのタイミングを扱うにはそれなりの高周波信号の基板設計が必要です。

しかし、とりあえず今回は、上手く動くかどうかは分かり

ませんが、できるだけ短い距離で配線しました。短くするため、ADコンバータはカメレオンUSBキットのコネクタCN1の裏面側に配置しています。

・現在、回路や電気配線などの理由で、ADコンバーターの変換は不完全な状

態です。ノイズがあり精度も出ていません。サンプリング周波数100MHzでは上手くうごきません。

■免責

(1)回路図やプログラムやデータの使用により、使用者に損失が生じたとしても、

その責任

を負いません。

(2)回路図やプログラムやデータにバグや欠陥があったとしても、修正や改良の義

務を負い

ません。